(This article has been originally published on December 10th, 2019 and has been edited on Feb 19th, 2020)

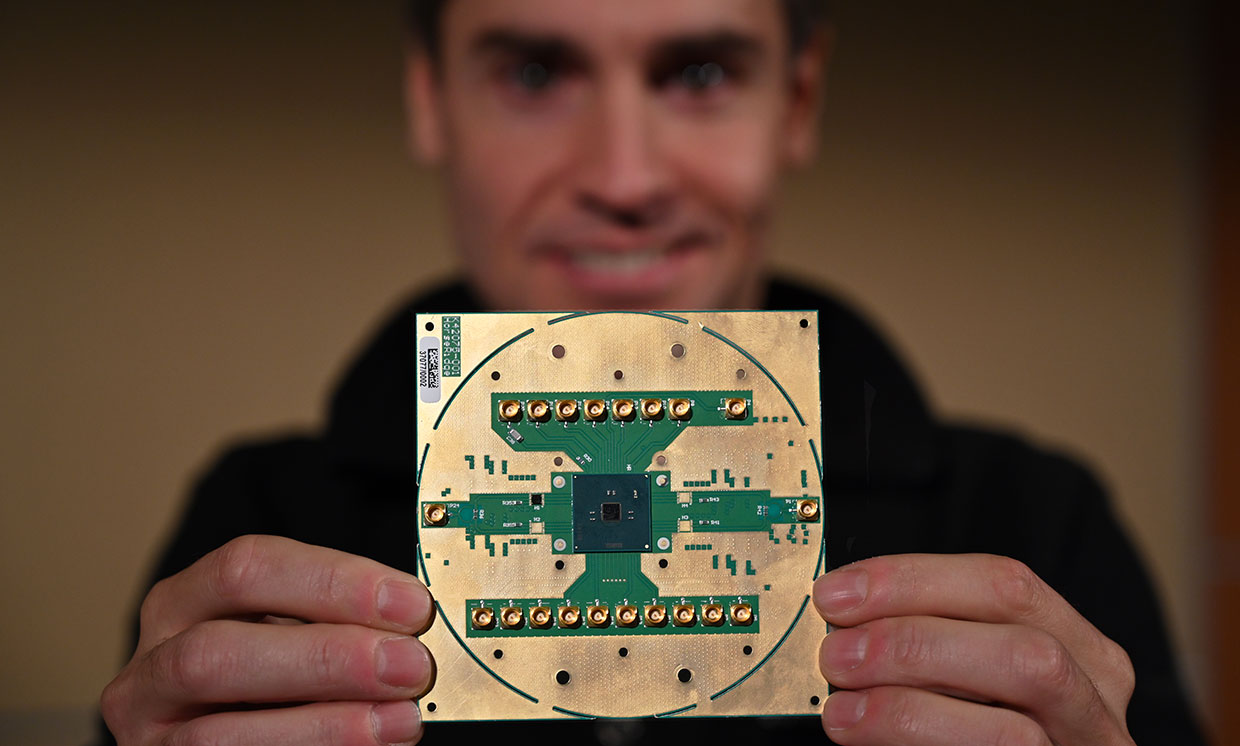

At the 2019 IEEE International Electron Devices Meeting in San Francisco, Intel unveiled a cryogenic chip designed to accelerate the development of the quantum computers they are building with Delft University’s QuTech research group. The chip, called Horse Ridge for one of the coldest spots in Oregon (the chip is designed to work at 3 kelvins) uses specially-designed transistors to provide microwave control signals to Intel’s quantum computing chips.

As scientists have managed to increase the number of qubits, they’ve begun to run into a problem. Each qubit needs its own set of wires leading to control and readout systems outside of the cryogenic container. It’s already getting crowded and as quantum computers continue to scale, there soon won’t be enough room for the wires.

Horse Ridge integrates control electronics onto a chip meant to operate inside the fridge with the qubit chip. Horse Ridge is programmed with instructions that correspond to basic qubit operations. It translates those instructions into microwave pulses that can manipulate the state of the qubits.

This CMOS integrated circuit is able to control up to 128 qubits and can therefore be described as a cryo-CMOS circuit.

The next challenge is to close the remaining temperature gap because spin qubits are expected to function at 1,5 K. If the researchers can bridge this temperature gap, they could integrate both qubits and their controlling electronics into the same package or chip, thus achieving an extremely compact system.

The paper and the presentation at ISSCC specifically describe the Intel 22-nm FFL FinFET cryo-CMOS controller that operates at 3 K over the wide band from 2 to 20 GHz and is able to drive up to 128 frequency-multiplexed spin qubits or transmons in a 1-GHz band. Qubit fidelity and performance are maximized by optimizing the generated output waveforms. Such extreme flexibility is enabled by the digitally-intensive architecture comprising a 180-kB SRAM for envelope storage, a digital polar modulator, a 1-GSa/s 10-bit I/Q DAC and a wideband RF front-end. For more information about the technical specifications of the cryo-CMOS controller, please refer to this fact sheet by Intel.

For Intel, Horse Ridge is a particularly important development, because it helps pave the way for the company’s next-generation qubit technology, called silicon spin qubits. (IEEE)